# A Highly Efficient And Reliable Inverter Configuration Based Cascaded Multi-Level Inverter For Pv Systems

SOORA MANORAMJAN<sup>1</sup>, K.SRINIVAS <sup>2</sup>, DAMALLA.BHAGYA PRASANNA<sup>3</sup> <sup>1</sup>Asst.Professor,EEE Dept, WITS Warangal, India <sup>2</sup>Asst.Professor &Head,EEE Dept,WITS Warangal.,India <sup>3</sup>M.TECH STUDENT, WITS Warangal, India

## **Abstract:**

This paper displays a enhanced Cascaded Multi-Level inverter (CMLI) dependent upon An profoundly proficient Also dependable setup to those minimization of the spillage present. Separated starting with a lessened switch count, those suggested plan need extra Characteristics of exchanging Furthermore conduction misfortunes. Those recommended toponomy with the provided for PWM procedure lessens the Highrecurrence voltage moves in the terminal Also common-mode voltages. Avoiding Highrecurrence voltage moves accomplishes the minimization of the spillage current Furthermore decrease in the extent of EMI filters. Furthermore, the development of the recommended CMLI alongside those PWM technobabble to 2m+1 levels may be likewise presented, the place m speaks to those amount for photograph Voltaic (PV) sources. Those suggested PWM strategy obliges main a absolute bearer

wave for the sum 2m+1 levels for operation. The aggregate symphonious twisting (THD) of the grid present for the recommended CMLI meets those necessities about IEEE 1547 standard. correlation of the suggested CMLI with those existing PV Multi-Level inverter (MLI) topologies will be also introduced in the paper. Complete subtle elements of the dissection of PV

terminal and common-mode voltages of the suggested CMLI utilizing exchanging capacity concept, simulations, Also test effects would exhibited in the paper.

**Keywords: Cascaded multi-level** inverter, leakage common-mode current, voltage, terminal voltage.

## 1. INTRODUCTION

TRANSFORMERLESS Multi-Level Inverter (MLI) topologies are picking up significance because of their points of interest, for example, high proficiency, low switch tally, low weight and decreased size. Notwithstanding, evacuation of the transformer takes out the galvanic confinement between the PV cluster and the yield stack. Evacuation of galvanic seclusion expands the spillage current trading off the wellbeing in PV frameworks. It has prompted the improvement of different security principles for the PV frameworks, which limit the esteem or extent of spillage current stream in the PV framework. Aside from spillage current minimization, there is a ceaselessly expanding interest for top notch control yield to be bolstered into the framework From the PV framework. This prerequisite has prompted the utilization of staggered inverters (MLI) in the transformer less PV frameworks. In writing, numerous topologies or arrangements of MLIs are proposed for the minimization of spillage current for their application in the transformer less PV frameworks. These arrangements utilize two strategies for minimization of the spillage current. One strategy depends on keeping up the basic mode voltage (CMV) steady, while the other technique depends on the minimization of the highrecurrence changes in the terminal and normal mode voltages.

One rich arrangement in view of keeping up a steady CMV. The given MLI arrangement comprises of eight switches for the age of three levels in the yield voltage. This topology decreases exchanging misfortunes yet has disadvantage of high conduction misfortunes amid both turn-ON and zero voltage states. The given MLI setup has a topsy-turvy activity amid every half-cycle of the key part of the framework voltage. The characteristic asymmetry in every half-cycle

causes a DC counterbalance in the MLI vield voltage. Besides, the prerequisite of an extra number of switches for more than three-level task restrains its application. have proposed another intriguing transformerless PV MLI topology to decrease the spillage current by keeping up CMV steady. This MLI topology utilizes six switches for the age of three levels in the inverter yield voltage. This circuit setup results in high exchanging and conduction misfortunes. Besides. this topology can't be stretched out to in excess of three levels in the yield voltage. have proposed another productive three-level MLI for the minimization of spillage current by keeping up CMV consistent. The given topology has low conduction and exchanging misfortunes. In any case, this design experiences the disservice of a high number of gadget check. Another fascinating topology with low exchanging misfortunes in view of consistent CMV .This MLI topology comprises of six switches and two diodes. Aside from bringing about high conduction misfortunes, this topology is less managable for an expansion to a higher number of levels in the yield voltage.

Another critical technique to limit the spillage current is by the end of high-recurrence voltage changes in the CMV. One such intriguing arrangement is proposed by Buticchi. The creators have proposed a nine-level lattice tied PV MLI topology. This MLI topology comprises of eleven switches and four diodes. In this MLI, four switches in the low voltage connect are worked with high exchanging.

### II. OPERATION **PROPOSED** OF **CASCADED FIVE-LEVEL MLI**

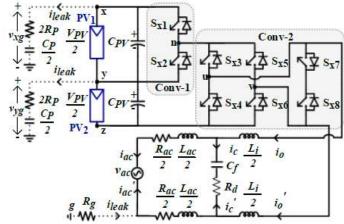

The schematic circuit outline of the proposed five-level CMLI for PV framework . The given design comprises of two converters (Conv-1 and Conv-2). Conv-1 is a half-connect inverter including two switches Sx1 and Sx2. The Conv-2 involves an exceedingly effective and solid inverter setup with six changes (Sx3 to Sx8). Among the six switches, four changes (Sx3 to Sx6) in Conv-2 constitute a H-connect circuit. The staying two switches Sx7 and S x8 in Conv-2 are bi-directional switches. The switches in the Conv-1 are utilized to produce the voltage levels of VPV and VPV/2. At the point when switch Sx1 is turned ON, the voltage VPV is connected at the terminal n as for the terminal z. So also, the terminal n

accomplishes the voltage VPV/2 when switch Sx2 is turned ON. The switches Sx1 and Sx2 are correlative in nature. The produced voltage levels at the terminal n of Conv-1 are given as a contribution to the Conv-2. The Conv-2 produces the positive, negative and zero levels of relating input (voltage between the terminals n and z) over the heap. The bi-directional switches Sx7 and Sx8 give the free-wheeling way amid zero voltage state. The yield of the five-level CMLI is associated with the framework through a LCL filter. It comprises of inverter side inductance Li, capacitance Cf and network side inductance Lac. The opposition Rd in the shunt branch of the channel is utilized as a damping resistor. The obstruction Rac alludes to the framework side opposition, and the opposition Rg shows opposition in the ground way. The variable vac alludes to momentary framework voltage. The factors Rp and Cp allude to the parasitic opposition and capacitance in the PV framework, individually appeared with dabbed lines. The parasitic capacitance in PV framework shapes a full circuit with the channel inductances

The factors io, ic and iac indicate the yield current of five-level CMLI, current coursing through shunt branch of the channel and the present streaming into the lattice separately. The current ileak demonstrates the spillage current spilling out of the PV cluster into the ground through parasitic capacitance

The proposed MLI topology contains four sets of reciprocal switches (Sx1, Sx2), (Sx3, Sx4), (Sx5, Sx6) and (Sx7, Sx8) in the proposed arrangement. Be that as it may, to limit the spillage current, the correlative exchanging is utilized just for the two sets of switches (Sx1, Sx2) and (Sx7, Sx8).

Fig. 1. Proposed five-level grid-connected CMLI with PV and parasitic

Keeping away from integral activity for alternate sets of switches helps in disconnecting the PV and the network source amid zero voltage state.

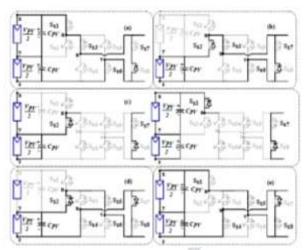

Fig. 2. Single Phase five-level cascaded MLI for output voltage levels (a)  $+V_{PV}$  (b)  $+V_{PV}/2$  (c)  $\theta$  (d)  $-V_{PV}/2$  (e)  $-V_{PV}$ . Fig. 2 demonstrates the activity of the inverter in the entirety of its exchanging states. The inverter yield voltage vuv at various voltage levels with the relating exchanging conditions of the considerable number of switches are appeared in Table I. The inverter yield voltage vuv achieves the voltage levels +VPV or – VPV when switch Sx1 is turned ON alongside other inverter switches (Sx3, Sx6) or (Sx4, Sx5) individually as appeared Essentially, the voltage levels +VPV/2 or - VPV/2 are gotten at vuv when switch Sx2 is turned ON with indistinguishable changing mixes from appeared. The most vital element to be seen amid zero voltage state or free-wheeling stage is the detachment or disengagement between PV source and the network. The segregation between the PV source and the matrix can be accomplished by killing every one of the switches of H-connect inverter as appeared.

The kill condition of four switches in Hconnect amid zero voltage state results in the segregation of PV source from the lattice. The bidirectional switches Sx7 and Sx8 give a freewheeling way to the inductor current amid the kill time of an exchanging cycle. This activity helps in limiting the spillage current moving through the parasitic capacitance. As there is no immediate association between the two sources, the PV terminal focuses (hubs x, y and z) glide and have indistinct voltages. The buoy or vague esteem limits the terminal voltages from getting to be zero. Therefore, high-recurrence voltage advances at the PV terminals are stayed away from. At the end of the day, the likelihood of the stream of spillage current can be limited. Additionally, in the other middle of the road states like exchanging between VPV/2 to VPV or the other way around, again a similar rule can be utilized. The above activity additionally helps in the minimization of the spillage current in the PV framework. The PWM strategy for the proposed five-level CMLI is comprehensively examined in segment . The articulation for the post voltages vuz and vvz are given below separately.

$$v_{uz} = \left(S_1 S_3 + 0.5 S_2 S_3 - \frac{1}{\left(S_3 + S_4\right)} + \frac{1}{\left(S_3 + S_4\right)\left(S_1 + S_2\right)}\right) V_{PV}$$

$$v_{vz} = \left(S_1 S_5 + 0.5 S_2 S_5 - \frac{1}{\left(S_5 + S_6\right)} + \frac{1}{\left(S_5 + S_6\right)\left(S_1 + S_2\right)}\right) V_{PV}$$

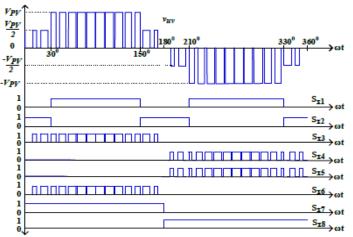

where Sa, (a=1, 2, 3...) is the exchanging condition of switch Sxa whose esteem can be either 1 (remains for turn-ON) or 0 (remains for kill) separately. demonstrates the exchanging example of the considerable number of switches for the comparing inverter yield voltage vuv. The switches Sx1 and Sx2 in the half-connect are worked at low exchanging recurrence. Keeping in mind the end goal to wipe out the high exchanging recurrence task, the switch Sx2 is kept turned ON in zero state amid voltage progress between the levels 0 to VPV/2. Essentially, the switch Sx1 is kept turned ON, amid voltage progress between levels 0 to VPV. The inverter switch combine (Sx3, Sx6) is worked with a high exchanging recurrence amid positive half-cycle, and it stays at the kill state amid the negative half-cycle of the inverter yield voltage vuv. A comparative activity is appropriate to the next inverter switch combine (Sx4, Sx5), which is worked with higher exchanging recurrence amid the negative half-cycle.

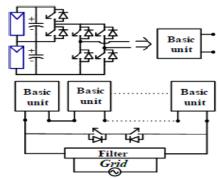

The summed up topology for 2m+1 levels can likewise be gotten for the proposed five-level CMLI. The quantity of PV sources in CMLI is signified by the term m. The estimation of m is dependably a necessary various of 2 (i.e., m =2, 4...). The broadened variant of the proposed CMLI for 2m+1 levels is displayed in Fig. 4. The summed up topology is acquired by falling the fundamental units comprising of half-extension and H-connect. The bi-directional switches are associated in the middle of the yield terminals for the free-wheeling time frame. The proposed

summed up 2m+1 level MLI is likewise contrasted and the half-scaffold and full-connect secluded staggered converter. The half-connect secluded staggered converter requires less number of changes when contrasted with the proposed summed up 2m+1 level MLI. Notwithstanding, it is hard to decrease or limit the stream of spillage current in the half-connect secluded staggered converter. Likewise, the quantity of electrolytic capacitors utilized at the information side of the half-connect

Fig. 3. Gate pulses for the switches corresponding to inverter output voltage.

#### III. PROPOSED PWM STRATEGY ALONG WITH GENERALIZED STRATEGY FOR THE **MINIMIZATION** OF LEAKAGE **CURRENT**

The operation of the proposed PWM technique is explained by considering the given five-level CMLI. The high-frequency transitions in the terminal voltages vxg and vyg of five-level CMLI are minimized using the proposed PWM technique. The suggested action can be achieved by switching from VPV to 0 state or vice-versa instead of the switching from VPV to VPV/2 state or vice-versa. Additionally, during the zero voltage state or free-wheeling period of the switching cycle, the PV array is isolated from the grid. The isolation of the PV array and the grid during zero voltage state is similar to the inverter configuration reported. The magnitude of reference wave *vmod* is lowered to 50% of its original value whenever the switching is toggled amongst the levels *VPV* and 0. The above action is mainly done to accommodate the value of PV voltage VPV.

Fig. 4. Generalized 2m+1 level MLI topology derived from proposed five-level CMLI.

The modification in the value of *ymod* is done whenever the instantaneous magnitude of modulating wave vmod exceeds the value of ma/2, where ma refers to the modulation index. By incorporating the desired modification, the output voltage includes the zero voltage state (i.e., free-wheeling state) in all its switching periods. The expression for modified reference waveform vref\_modified

$$v_{ref\_modified} = \begin{cases} v_{mod} & for \quad 0 \le |v_{mod}| < \frac{m_a}{2} & from \quad \frac{V_{PV}}{2} to \ 0 \\ \frac{v_{mod}}{2} & for \quad \frac{m_a}{2} \le |v_{mod}| < m_a \quad from \ V_{PV} to \ 0 \end{cases}$$

where, vmod= mama sinot gives the extent of vmod.

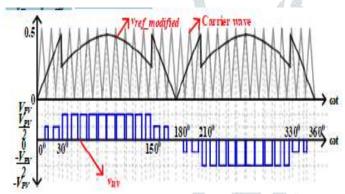

The yield voltage of the proposed PWM method for the five-level CMLI is appeared the changed reference wave is contrasted and the triangular transporter wave. Amid the positive halfcycle of voltage vac, at whatever point the stage edge of lies in extend 00 to 300 and the momentary greatness of vref\_modified surpasses the bearer wave, at that point vuv achieves the voltage level of VPV/2 else, it is exchanged zero voltage state. Also, when ωt lies in the range 300 to 1500, the inverter yield voltage vuv accomplishes the voltage level of VPV at whatever point the momentary extent vref\_modified surpasses the transporter wave or achieves zero esteem generally. In a similar positive half-cycle, for the rest of the scope

of ωt (i.e., between 1500 to 1800), vuv achieves the voltage levels VPV/2 if the immediate extent of vref\_modified is more noteworthy than the bearer wave. A comparative succession is received amid the negative half-cycle of voltage vac. Hence, in the total cycle if the extent of vref\_modified is not as much as the bearer wave, at that point vuv achieves zero voltage level.

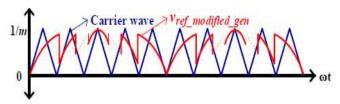

For the execution of the proposed PWM to a 2m+1 level inverter, the waveform of summed up adjusted reference wave vref\_modified\_gen is appeared in Fig. 6. The term m alludes to the quantity of PV sources utilized. At whatever point the immediate outright greatness of vmod surpasses the esteem j(ma/m), the extent of vref\_modified\_gen progresses toward becoming k(|vmod|/m) where j = 1, 2, ..., m-1, m and k = 1, 2, ...... m-1. The articulation for the vref\_modified\_gen is given in (4).

Fig. 5. The waveform of output voltage  $v_{UV}$  for the proposed PWM technique

#### IV. INTEGRATION **OF MPPT FOR** PROPOSED FIVE-LEVEL CMLI

The well-known perturb and observe algorithm is employed for the two PV sources (considering five-level

activity) independently to track Maximum Power Point (MPP). In this manner, each MPPT calculation tracks the MPP for individual PV sources. To track the MPP, the required data of the normal estimations of the two PV source voltages (VPV1 and VPV2 for the PV sources PV1 and PV2 separately)the streams (IPV1 and IPV2 for the PV

sources PV1 and PV2 individually) are detected and after that given to their particular MPPT calculations. The MPPT calculations at that point utilize the detected estimations of the PV voltages and streams for the count of the individual estimations of the adjustment records ma1 and ma2 for the two PV sources PV1 and PV2 separately. The yields of two MPPT calculations are then used for the computation of in general balance record mama. The articulation for mama is given in

## SIMULATION RESULTS

Fig. 6. Proposed five-level CMLI integrated with MPPT. The subplots give waveforms of : (a) voltage VPV1; (b) voltage V<sub>PV2</sub>; (c) current I<sub>PV1</sub>;

(d) current IPv2; (e) power PPv1; (f) power PPv2; (g) resultant modulation index ma; (h) output power P out, (i) modified reference wave Vref\_modified;

(j)inverter output voltage vab.

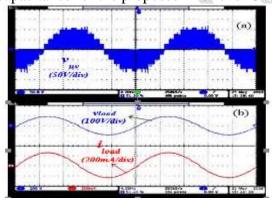

Fig. 7. The experimental waveforms of : (a) switching functions of switches  $S_{x1}$ ,  $S_{x3}$ ,  $S_{x4}$ ,  $S_{x5}$ ,  $S_{x6}$ ,  $S_{x7}$ ; (b) output voltage  $v_{uv}$ ; (c) voltage  $v_{load}$ across and current  $i_{load}$  flowing through resistive load; (d) terminal voltage waveforms of  $v_{xg}$ ,  $v_{yg}$  and  $v_{zg}$ ; (e) leakage current  $i_{leak}$  in the parasitic capacitance for the proposed five-level CMLI.

Fig. 8. The experimental waveforms of ninelevel CMLI: (a) output voltage  $v_{uv}$ ; (b) voltage  $v_{load}$  across and current  $i_{load}$  flowing through the resistive load.

## V. CONCLUSION

In this paper, an enhanced five-level CMLI with low switch mean the minimization of spillage current in a transformerless PV framework is

proposed. The proposed CMLI limits the spillage current by wiping out the high-recurrence changes in the terminal and normal mode voltages. The proposed topology additionally has diminished conduction and exchanging misfortunes which makes it conceivable to work the CMLI at high exchanging recurrence. Besides, the answer for summed up 2m+1 levels CMLI is likewise introduced in the paper. The given PWM strategy requires just a single transporter wave for the age of 2m+1 levels. The task, examination of terminal and normal mode voltages for the CMLI is additionally introduced in the paper. reproduction and trial results approve examination did in this paper. The MPPT calculation is likewise coordinated with the proposed five-level CMLI to remove the greatest power from the PV boards. The proposed CMLI is likewise contrasted and the other existing MLI topologies in Table V to demonstrate its focal points.

## REFERENCES

[1] Y. Tang, W. Yao, P.C. Loh and F. Blaabjerg, "Exceptionally Reliable Transformerless Photovoltaic Inverters With Leakage Current and Pulsating Power Elimination," IEEE Trans. Ind. Choose., vol. 63, no. 2, pp. 1016-1026, Feb. 2016.

[2] W. Li, Y. Gu, H. Luo, W. Cui, X. He and C. Xia, "Topology Review and Derivation Methodology of Single-Phase Transformerless Photovoltaic Inverters for Leakage Current Suppression," IEEE Trans. Ind. Choose., vol. 62, no. 7, pp. 4537-4551, July 2015.

[3] J. Ji, W. Wu, Y. He, Z. Lin, F. Blaabjerg and H. S. H. Chung, "A Simple Differential Mode EMI Suppressor for the LLCL-Filter-Based Single-Phase Grid-Tied Transformerless Inverter," IEEE Trans. Ind. Choose., vol. 62, no. 7, pp. 4141-4147, July 2015.

[4] Y. Bae and R.Y.Kim, "Concealment of Common-Mode Voltage Using a Multicentral Photovoltaic Inverter Topology Synchronized PWM," IEEE Trans. Ind. Choose., vol. 61, no. 9, pp. 4722-4733, Sept. 2014.

[5] N. Vazquez, M. Rosas, C. Hernandez, E. Vazquez and F. J. Perez-Pinal, "A New Common-Mode Transformerless Photovoltaic Inverter,"

IEEE Trans. Ind. Choose., vol. 62, no. 10, pp. 6381-6391, Oct. 2015.

[6] G. Buticchi, E. Lorenzani and G. Franceschini, "A Five-Level Single-Phase Grid-Connected Converter for Renewable Distributed Systems," IEEE Trans. Ind. Choose., vol.60, no.3, pp.906-918, March 2013.

[7] N.A. Rahim and J. Selvaraj, "Multistring Five-Level Inverter With Novel PWM Control Scheme for PV Application," IEEE Trans. Ind. Choose., vol.57, no.6, pp.2111-2123, June 2010.